# ANALYZING THE PERFORMANCE OF A HYBRID 1-BIT FULL ADDER CIRCUIT WITH LOW POWER CONSUMPTION AND HIGH SPEED

Mr. Mohammed Imran\*1, Dr. Amairullah Khan Lodhi\*2, Dr. Mohammad Iliyas \*3

\*1 PG Student Dept. of ECE (VLSI System Design), Shadan College of Engineering and Technology

Mohammedimran10124@gmail.com

\*2 Professor, R & D Coordinator, Dept. of ECE, Shadan College of Engineering and Technology lak\_resumes@yahoo.com (D

\*3 Professor & HOD, Dept. of ECE, Shadan College of Engineering and Technology ilyas.ece@gmail.com

Abstract: In this endeavor, across a variety of 1-cycle, full snake setups using both comparing metal-oxide-semiconductor (CMOS) reasoning and transmission entryway reasoning is represented. The arrangement was first completed for 1 cycle and thereafter loosened up for 32 digits besides. The circuit was completed using Cadence Virtuoso contraptions in 180-and 90-nm advancement. Execution limits like power, deferral, and configuration district were differentiated and the current plans, for instance, comparing pass-semiconductor reasoning, transmission entrance snake, transmission work snake, creamer pass-reasoning with static CMOS yield drive full snake, and so forth For 1.8-V stock at 180-nm advancement, the ordinary power usage (4.1563  $\mu$ W) was seen as amazingly low with humbly low deferral (224 ps) coming about as a result of the deliberate wire of incredibly fragile CMOS inverters joined with strong transmission entryways. Looking at potential gains of the comparable were 1.17664  $\mu$ W and 91.3 ps at 90-nm development working at 1.2-V stock voltage. In relationship with the current full snake designs, the current execution was found to offer basic improvement to the extent that power and speed.

**Index Terms**— Carry propagation adder, high speed, hybrid design, low power.

#### 1. INTRODUCTION

VLSI signifies "Incredibly Large Scale Integration". This is the field that incorporates squeezing progressively more reasoning contraptions into progressively little areas. VLSI, circuits that would have taken boards of space can now be put into a little space relatively few millimeters across! This has opened up a significant entryway to do things that were illogical beforehand. VLSI circuits are everywhere .your PC, your vehicle, your crisp out of the plastic new state-of-the-art progressed camera, the cells, and what have you. This remembers a lot of expertise for some fronts inside the comparative field, which we will look at in later regions. VLSI has been around for a long time, but because of advances in the domain of PCs, there has been a shocking increase in devices that can be used to arrange VLSI circuits. Nearby, consenting to Moore's guideline, the limit of an IC has extended drastically all through the long haul, to the extent that estimation power, utilization of available area, yield. The united effect of these two advances is that people can now put different helpfulness into the Ic's, opening up new edges. Models are introduced systems, where brilliant contraptions are put inside conventional things, and ubiquitous figuring where little enrolling devices duplicate such a lot of that even the shoes you wear may truly achieve something accommodating like noticing your heartbeats. Consolidated circuit

(IC) development is the engaging advancement for a whole host of innovative devices and systems that have changed the way wherein we live. Jack Kilby and Robert Noyce got the 2000 Nobel Prize in Physics for their formation of the organized circuit; without the consolidated circuit, neither semiconductors nor PCs would be anyway critical as they appear to be today. VLSI systems are significantly more humble and consume less power than the discrete parts used to develop electronic structures before the 1960s. Compromise licenses us to build systems with significantly more semiconductors, allowing considerably seriously handling capacity to be applied to handling an issue. Composed circuits are similarly significantly more direct to plan and deliver and are more strong than discrete systems; that makes it possible to encourage specific explanation structures that are more viable than extensively valuable PCs for the principle work.

#### 1.1 ADVANTAGES OF VLSI

While we will zero in on composing circuits in this book, the properties of consolidated circuits that we can and can't put in a fused circuit generally choose the plan of the entire system. Facilitated circuits further foster structure characteristics in a greater number of ways than one. I appreciate three basic high grounds over automated circuits worked from discrete parts:

- Size. Composed circuits are much more unobtrusive the two semiconductors and wires are contracted to micrometer sizes, standing out from the millimeter or centimeter sizes of discrete parts. Little size prompts benefits in speed and power use since more unobtrusive parts have more unassuming parasitic assurances, capacitances, and inductances.

- Speed. Signs can be traded between reasoning 0 and reasoning 1 a lot quicker inside a chip than they can between chips. Correspondence inside a chip can happen commonly faster than correspondence between chips on a printed circuit load up. The high speed of circuits on-chip is a result of their little size-more unassuming parts and wires have more humble parasitic capacitances to tone down the transmission.

- Power usage. Reasoning errands inside a chip similarly take extensively less power. Once lower power usage is generally a direct result of the little size of circuits on the chip-more unobtrusive parasitic capacitances and securities require less capacity to drive them.

## 1.2. ROUTING

The arranging framework picks the specific ways for interconnections. This merges the standard cell and gigantic expansion sticks, the pins on very far or pads past what many would think about conceivable. After a strategy and CTS, the instrument has information about the particular areas of squares, pins of squares, and I/O pads at chip limits. The expected relationship as portrayed by the netlist is furthermore open to the mechanical social affair. In the getting sorted out stage, metal and vias are used to make the electrical relationship in arrangement to complete all affiliations portrayed by the netlist. Now, to do the authentic interconnections, the contraption relies on some "Plan Rules".

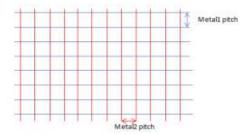

Most of the switches open are network-based switches. There are arranging lattices portrayed for the entire course of action. Consider it as a plan as under. For structure-based switches, there are moreover preferred controlling headings portrayed for each metal layer. for instance, Metal1 has an inclined in the direction of the course of "level', metal2 has truly leaned toward coordinating heading of "vertical, and so on Along these lines,

in the whole course of action, metal1 arranging affiliations will be drawn (superimposed) on a level plane with metal1 wire pitch and metal2 cross-regions will be drawn vertical with metal2 wire pitch between each.

Figure 1: Routing Grids

The above figure shows how coordinating grids are drawn. Here only two metals are considered for the present, but in a cycle with more metals, relative structures will be superimposed on the organization for each available metal. Not entirely settled by concluding the base scattering expected between system lines of the same metal.

This can be the base scattering of the metal but is by and large a value more imperative than the base isolating. Not set in stone by considering the through viewpoint additionally, with the objective that no two connecting wires on the cross-section make any DRC encroachment regardless when there are vias present.

## 2. Experience and Assessment:

Our transitory work range was of a half year. Immediately when we started, classes were coordinated and I acquired various thoughts as indicated by present-day viewpoint and liked them executing all things considered. Then, our affiliation had embraced projects from St. Mary's school, Hyderabad, a piece of those errands were done by me and I went to the show in that school and connected with students for our affiliation.

The inclusion with the association was pleasant, people work in co-arrangement and the association environment is especially safeguarded and studios. The inspiration to pick this association was that it was offering section level situation in VLSI which is my middle specialization in PG degree and I expected to benefit from this experience, in like manner I got to learn new instruments like Electric, Symica DE, and Microwind.

I used to spend just about 5 to 6 hours consistently in the association offering a chance with different circuits and making their arrangements genuinely. I thank my helper who was, by and large, there nearby all through my brief work process offering me direction, information, and tips on how people work in an industrial environment.

A couple of specific outcomes are:

VLSI chip's application is for the most part for mobile phones which are dependent upon having a longer battery span. Likewise, the new electronic things require extended value, first-class execution, and coordination of a

colossal number of parts inside a lone chip provoking power-consumed plans. So how to make the chip lower power is essential for the association.

The goals of a chipmaker are:

- To reduce power use.

- To lessen district.

- To accelerate and execution of the chip.

A couple of non-specific outcomes are:

- The assurance level is extended.

- Stage fear vanishes.

- I have encouraged the ability to explain my viewpoint to the front individual clearly.

- I discovered how things will be finished in a certified industry.

## **4.2 Contribution to the Organization:**

During my brief work, I expected to add to the association's endeavors by applying the data which I have procured during my entry-level position learning process. So I have contributed by arranging a low power-area capable 1 digit full snake using the gadget Microwind2.

## 3. Low Power-Area Efficient Design of 1 cycle Full Adder:

In the nanometer setup plan, spillage power has a major need of complete power. The use of power has been extended as in a general sense significant in the piece of the plan for each Integrated Circuits(IC). On an extra note is a significant number of shuffling movements are used occasionally in a colossal degree as well as extraordinarily enormous extension blend application arranged DSP and central processor plans. The Full snake circuit arrangement is especially crucial and to be a certain unit of an ALU, which picks the structure's overall direction. The power use of a processor depends upon the ALU, so the power consumed by the full snake circuit in the ALU should get somewhat decreased to facilitate the necessities of an organizer in this way it will be called "a less filled arrangement".

#### 4. Some of the Conventional Full Adder Designs

The low power full snake plans have been arranged and done by various XOR and XNOR modules. The reasoning of DOMINO and PTL drives the organizer to design a full snake with low power and deferment. In the full snake plan thoughts, the SERF (Static energy recovery Adder) plan and GDI (Gate Diffusion Input) techniques were ordinary. To diminish the power fairly the Pseudo NMOS reasoning is used with an inverter. To make the outcome that is the pass in faster mean and on to diminish power concede thing the sub edge 1-bit full snake and combination CMOS styles have been used. The proposed arrangement will be under Pass semiconductor reasoning and the benefit of using PTL is its quick movement since it has less center capacitance. As the amount of semiconductors is lessened the power scattering is less and the effects of interconnection are particularly low however it in like manner consumes less area.

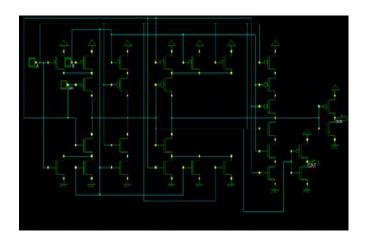

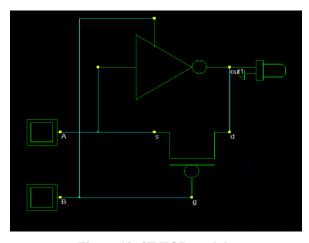

Figure 2: Schematic of Conventional Full Adder.

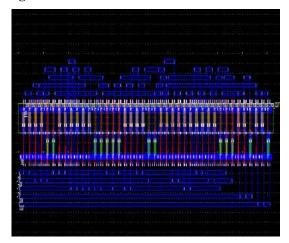

Figure 3: Layout of Conventional Full Adder.

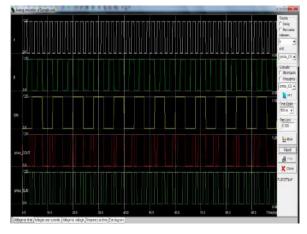

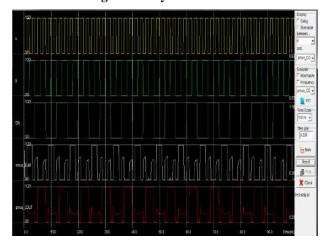

Figure 4: Layout Simulation of Conventional Full Adder.

In this section, several different designs of low power and high speed adders are introduced. The Static recovery adder(Figure 4) is the extreme low power design because in this design there will be direct contact path between supply and ground terminal and it also can re-apply the load charge to the gate terminal as control(energy recovery)Figure 4.

Figure 4: Schematic of SERF.

Figure 5: Layout of SERF.

Figure 6: Layout Simulation of SERF.

Chowdhryet al. proposed a novel 8T full adder circuit shown in figure 7.

Figure 7: 8T Full Adder design

The low voltage operation, high computation speed and low delay degradation have been attained by using complementary and carry restoring logic.

Figure 8: Layout of 8T Full Adder.

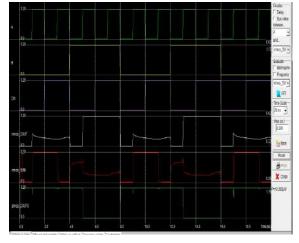

Figure 9: Layout Simulation of 8T Full Adder.

The design adopts inverter buffered XOR/XNOR designs to console the threshold voltage loss problem. However, most of the Pass transistor logic commonly causes two main problems. First one is that, slow operation at reduced voltages due to the threshold drop across the single-channel pass transistors. It also reduces the current drive, since it is desirable to operate at very low possible operating voltage level which is specifically for the low power design.

Secondly, since the "high" input voltage level is not at the regenerative inverters, the inverter's PMOS is not fully turned off, so the direct-path static power dissipation could be significant. So I have designed a new full adder circuit consisting maximum of 6T which is analyzed and compared with earlier technique adder circuits.

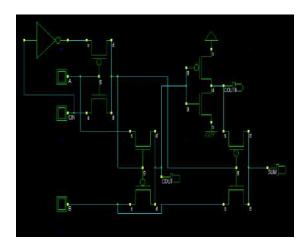

#### 4.1 Design of 6T Full Adder Circuit

The full adders of various designs of less transistor count will be in use of 3- module implementations that is XOR or XNOR for both sum as well as carry generating modules.

This full adder design is of low powered and transistors of less count which is verified using Microwind simulations. The circuit design is of 6T and with pass transistor logic. The power of this circuit is tremendously less when compared to the conventionally designed adder circuit which is of 28T and 8T static and energy recovery full adder (SERF) design, whereas the delay is comparatively less.

The design of PTL based technique will be required 4 transistors in least to design a XOR or XNOR model, but this design results in extreme threshold voltage loss problems. The main concern of this design is to use the Tristate inverter in the place of normal inverter which have been used for all low power designed circuits, because of the power consumption of the tri state inverter is less compared to normal one. This results in low operation throughput and average leakage of the circuit. Normally the inverter's supply voltage is HIGH always; whereas in Tristate inverter the supply voltage is not always HIGH. This reduces the operation throughput and average leakage of the circuit. Figure 4.11 shows the Tristate inverter.

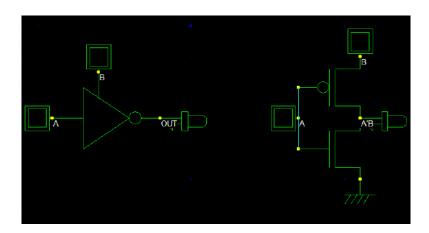

Figure 10: 3T XOR module

Figure 11: Tristate inverter

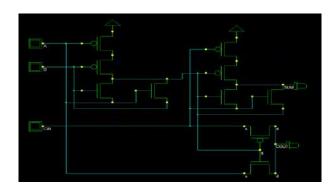

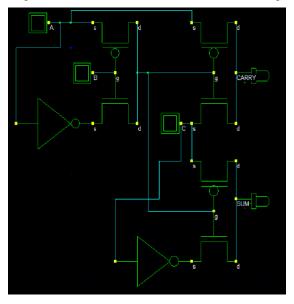

# 4.2 Proposed 6T full adder design

In the proposed 6T full adder sum is generated using 2 transistor XOR module twice, PMOS and NMOS is used to generate the carry. The below equations for Proposed 6T are,

Sum =

$$(a \text{ xor } b) \text{ xor } c$$

$\Rightarrow (a \text{ xor } b) c' + (a \text{ xor } b)'c$

Carry =  $ab + bc + ca$

$\Rightarrow (a \text{ xor } b)'a + (a \text{ xor } b)c$

In this design (a XOR b) signal is passed to the pass transistor based multiplexer made of two transistors to choose one among two signals. To generate carry (a XOR b) is sent to multiplexer to choose between a, c and to generate sum (a XOR a) is sent to choose between c', c. This simulation results comparatively less power consumption than the earlier designs whereas it is also used in Arithmetic and logic unit design.

Figure 12 Proposed 6T Full Adder.

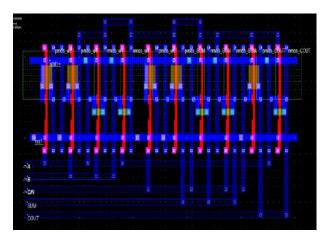

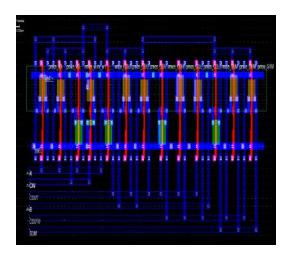

Figure 13 Layout of Proposed 6T Adder

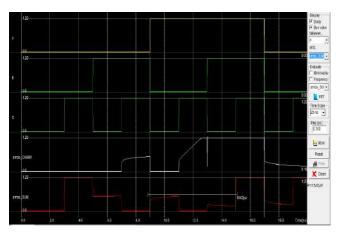

Figure 14 Layout Simulation of Proposed 6T Adder.

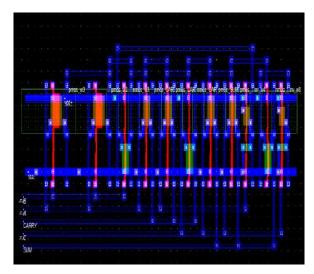

# 5. Result and Comparison

The entire simulations have been done on Microwind 2 for the power estimation and the consolidated results are compared with different techniques. The area is reduced tremendously when compared to 28T conventional full adder and SERF adder design.

**Table 1 Simulation Results**

| Full adder designs | Conventional | Chowdery et all | SERF    | Proposed |

|--------------------|--------------|-----------------|---------|----------|

|                    | 28T          | (8T)            |         | 6T       |

| Average power      | 22.569μW     | 10.453μW        | 3.984µW | 1.547μW  |

| consumption        |              |                 |         |          |

| No. of transistors | 28           | 8               | 10      | 6        |

#### 6. Conclusion and Future Work

The diversion delayed consequences of the proposed full snake have been differentiated and the previous plans like common (28T), SERF (10T), Novel arrangement (8T) using Microwind gadget. According to the diversion, the proposed circuit consumes less power than the past arranged circuits missing a great deal of result corruption.

The proposed full snake circuit will be executed in the mood virtuoso stage. The arrangement can be used for Modified Booth Multiplier Circuit for recoding the Multiplicand and divider circuits moreover.

Also, the open-source Microwind VLSI Design System is not difficult to utilize programming to be used in arranging the configuration of any high-level circuit. It is generally expected that the item can adjust to a more multifaceted modernized IC arrangement with its set-up of check and set up instruments.

The brief position program was extremely invaluable to me. I learned different specific points which were associated with our instructive program, besides these, there were non-particular locales in which I cultivated an extraordinary arrangement. It was a fantastic experience working with specialists and partnering with them, acquiring from their experience and working under their course. I similarly liked concurring with the shows of the affiliation. I mastered staggering ability on the total.

#### REFERENCES

- [1] P. Reyes, P. Reviriego, J. A. Maestro, and O. Ruano, "New security systems against SEUs for moving typical diverts in a radiation environment," IEEE Trans. Nucl. Sci., vol. 54, no. 4, pp. 957-964, Aug. 2007.

- [2] M. Hatamian et al., "Plan examinations for gigabit ethernet 1000 base-T reshaped pair handsets," Proc. IEEE Custom Integr. Circuits Conf., pp. 335-342, 1998.

- [3] H. Yamasaki and T. Shibata, "A consistent picture feature extraction and vector-age VLSI using showed shift-register designing," IEEE J. Solid-State Circuits, vol. 42, no. 9, pp. 2046-2053, Sep. 2007.

- [4] H.- S. Kim, J.- H. Yang, S.- H. Park, S.- T. Ryu, and G.- H. Cho, "A 10-digit section driver IC with parasitic-inhumane iterative charge-sharing based capacitor-string inclusion for flexible powerful lattice LCDs," IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 766-782, Mar. 2014.

- $\cite{Model}$  S.- H. W. Chiang and S. Kleinfelder, "Scaling and plan of a 16-megapixel

- CMOS picture sensor for electron microscopy," in Proc. IEEE Nucl. Sci. Symp. Conf. Record (NSS/MIC), 2009, pp. 1249-1256.

- [6] S. Heo, R. Krashinsky, and K. Asanovic, "Activity fragile flip-flop moreover lock assurance for decreased energy," IEEE Trans. Extraordinarily Large Scale Integr. (VLSI) Syst., vol. 15, no. 9, pp. 1060-1064, Sep. 2007.

- [7] S. Naffziger and G. Hammond, "The execution of the next-generation 64 b Itanium chip," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2002, pp. 276-504.

- [8] H. Partovi et al., "Course through lock and edge-set off flip-flop cream parts," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 138-139, Feb. 1996.

[9] E. Consoli, M. Alioto, G. Palumbo, and J. Rabaey, "Unexpected push-pull beat snare with 726 flops energy concede thing in 65 nm CMOS," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2012, pp. 482-483.

[10] V. Stojanovic and V. Oklobdzija, "Comparable assessment of master-slave snares and flip-flops for predominant execution and low-power systems," IEEE J. Solid-State Circuits, vol. 34, no. 4, pp. 536-548, Apr. 1999.

#### **AUTHOR PROFILE**

**Mr. MOHAMMED IMRAN,** M.Tech student in ECE (VLSI System Design) from Shadan College of Engineering And Technology, Peerancheru, Telangana.

**Dr. AMAIRULLAH KHAN LODHI, Professor,R & D Coordinator,** Dept. of ECE from Shadan College of Engineering and Technology, Peerancheru, Telangana.

**Dr. Mohammad Iliyas** working as Professor & HOD of ECE Department at Shadan College of Engineering and Technology, Hyderabad. He received his Bachelor degree in Electronis and Communication Engineering from J.N.T.U.H affiliated college, Hyderabad, M.Tech, V.L.S.I System Design from J.N.T.U.H affiliated college. He has completed Ph.D from Sunrise University. His research interest is Low power VLSI Design.