# PULSEREG: A NOVEL SHIFT REGISTER DESIGN WITH PULSED LATCHES FOR ENHANCED POWER AND AREA EFFICIENCY

# Ms. NAGAMANI MOUNIKA\*1, Dr. MOHAMMAD ILIYAS \*2 Dr. AMAIRULLAH KHAN LODHI \*3,

\*1 PG Student Dept. of ECE (VLSI System Design), Shadan College of Engineering and Technology nagamanimounika7890@gmail.com

\*2 Professor & HOD, ECE Department. and Dean (Academics), Shadan College of Engineering and Technology ilyas.ece@gmail.com

\*3 Professor, ECE Department. Dean (R & D), Shadan College of Engineering and Technology lak\_resumes@yahoo.com

Abstract: This project proposes a novel and energy-efficient approach for implementing a low-power and areaefficient shift register using beat snares. By incorporating beat locks to override flip-flops, the proposed design minimizes both the area footprint and energy consumption. Unlike traditional systems that rely on a single beat clock signal, this approach utilizes a range of nand on-overlapping delayed beat clock signals to address timing issues between beat locks. By distributing the snares among a small number of sub-shifter enlistees and employing temporary storage locks, the move register significantly reduces the dependency on beat clock signals. To construct a 256-cycle move register with beat locks, a 0.18m CMOS process with VDD = 1.8V was employed. The implementation occupied an optimized area of 6600 sq. ft. At a clock frequency of 100 MHz, the power consumption was measured to be 1.2mW. Comparative analysis demonstrated that the suggested move register could potentially save up to 37% of the required area and 44% of the required power compared to a conventional move register built with flip-flops. A move register is a circuit comprised of interconnected flip-flops, all driven by a common clock signal. Each flip-flop's output is connected to the "data" input of the subsequent flip-flop in the sequence. This arrangement enables the circuit to shift the stored "piece display" by one position on every clock edge, introducing new data at its input and releasing the last piece in the sequence. In a broader context, a move register can have multiple dimensions, where both the input data and output stages consist of bit arrays. This can be achieved by employing multiple move registers with the same bit length in parallel.

**Keywords:** Shift registers, Flip-flop, Pulsed latches, Low power, Efficient area

## **INTRODUCTION**

A shift register is the central design block in a VLSI circuit. Move registers are usually used in various applications, for instance, modernized channels, correspondence authorities, and picture planning ICs, Starting late, as the size of the image data continues extending on account of the interest for great picture data, the word length of the shifter register additions to deal with tremendous picture data in picture

ISSN: 2456-4265 IJMEC 2024

13

Volume 9, Issue 02, February-2024, http://ijmec.com/, ISSN: 2456-4265

planning ICs. Image extraction and vector age VLSI chip use a 4K-piece move register. A 10-digit 208 channel yield LCD fragment driver IC uses a 2K-cycle move register. A 16-megapixel CMOS picture sensor uses a 45K-piece move register. As the word length of the shifter register assembles, the zone and power use of the move register become huge arrangement considerations.

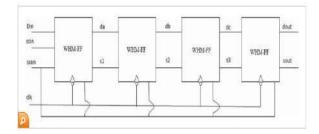

The design of a move register is clear. An N-digit move register is made out of game plan related N data flip-flops.

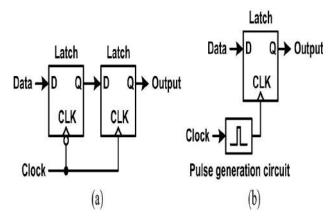

The speed of the flip-flop is less huge than the region and power use because there is no circuit between flip-flips in the move register. The smallest flip-flop is fitting for the move register to reduce the zone and power use. Starting late, beat snares have displaced flip-flops in various applications, considering the way that a beat lock is significantly more unobtrusive than a flip-flop.

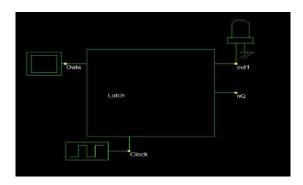

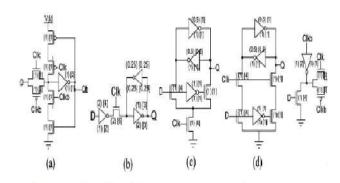

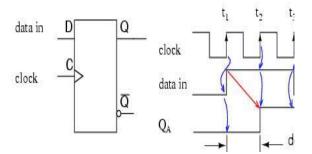

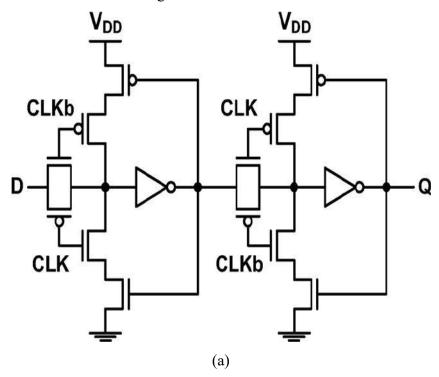

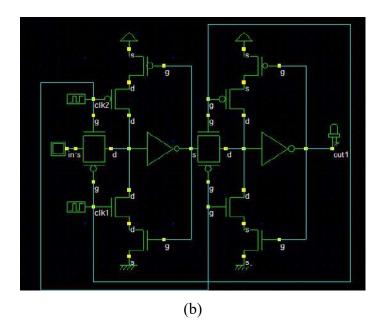

Figure 1: (a) Master-slave flip-flop. (b) Pulsed latch.

Figure 1.1: Schematic diagrams of (a) master-slave flip flop. (b) Pulsed latch.

This paper proposes a low-power and area beneficial move register using beat locks. The move register handles the situation issue using diverse non-cover conceded beat clock hails as opposed to the normal single beat clock signal. The move register uses not many of the beat clock signals by get-together the snares to a couple of sub shifter enlists and using extra ephemeral storing locks.

Move registers can have both equivalent and successive data sources and yields. These are oftentimes organized as 'consecutive in, equivalent out' (SIPO) or as 'equivalent in, successive out' (PISO). There are furthermore types that have both successive and equivalent data and types

with consecutive and equivalent yields. There are in like manner 'bidirectional' move registers which grant moving in the two different ways:  $L \rightarrow R$  or  $R \rightarrow L$ . The consecutive data and last yield of a move register can similarly be related with make an 'indirect move register'.

Some particular counter circuits truly use move registers to create repeating waveforms. Longer move registers, with the help of analysis, make plans so long that they look like the sporadic upheaval, pseudo-uproar.

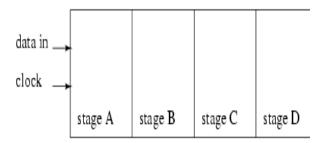

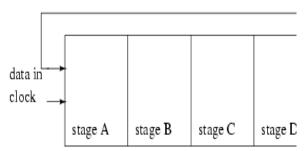

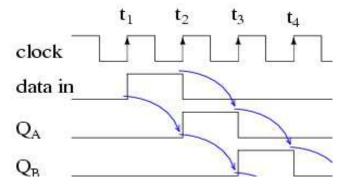

Above we show a square diagram of a consecutive in/successive out moves register, which is 4-sorts out long. Data at the data will be deferred by four clock periods from the commitment to the yield of the move register.

Data at "data in", above, will be accessible at the Stage A yield after the chief clock beat. After the ensuing heartbeat stage A data is transferred to orchestrate B yield, and "data in" is transferred to put together A yield. After the third clock, stage C is replaced by stage B; stage B is displaced by stage A, and stage An is superseded by "data in". After the fourth clock, the

data at first present at "data in" is at stage D, "yield". The "first in" data is "first-out" as it is moved from "data in" to "data out".

Data is stacked into all stages immediately of an equivalent in/successive out move register. The data is then moved out by methods for "data out" by clock beats. Since a 4-stage move register is showed up more than, four clock beats are expected to move out the aggregate of the data. In the chart above, stage D data will be accessible at the "data out" up until the principle clock beat; stage C data will be accessible at "data out" between the chief clock and the ensuing clock beat; stage B data will be accessible between the resulting clock and the third clock, and stage A data will be accessible between the third and the fourth clock. After the fourth clock beat and starting there, reformist bits of "data in" should appear at "data out" of the move register after a delay of four clock beats.

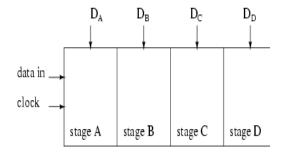

If four switches were related with DA through DD, the status could be added a bonus to a chip using simply a solitary data pin and a clock pin. Since adding more switches would require no additional pins, this procedure looks engaging for certain wellsprings of information.

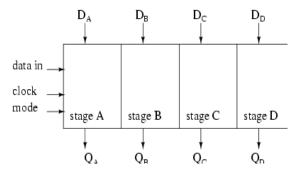

More than, four data pieces will be moved in from "data in" by four clock beats and be open at QA through QD for driving external equipment, for instance, LEDs, lights, hand-off drivers, and horns.

After the essential clock, the data at "data in" appears at QA.

ISSN: 2456-4265

16 **IJMEC 2024**

After the resulting clock, The old QA data appears at QB; QA gets the next data from "data in". After the third clock, QB data is at QC. After the fourth clock, QC data is at QD. This stage contains the data first present at "data in". The move register should now contain four data bits

An equivalent in/equivalent out move register joins the limit of the equivalent in, successive out move register with the limit of the consecutive in, equivalent out move register to yield the boundless move register. The "do anything" shifter incorporates some significant disservices the extended number of I/O (Input/Output) pins may diminish the number of stages which can be packaged.

If the successive yield of a move register is related to the consecutive data, data can be on and on moved around the ring to the extent that clock beats are accessible. If the yield is turned around before being dealt with back, as shown above, we don't have to worry about stacking the hidden data into the "ring counter".

Figure 1: Fig. 1. High-enabled latch designs. Transistor sizes are shown for a low-power design (in parentheses: ( )) and a high-speed design (in brackets: [ ]). A transistor labeled with size n means that its W/L ratio is n times that of a minimum-sized transistor. For gates, the sizes of all transistors are shown. (a) PPCLA. (b) PTLA. (c) SSALA. (d) SSA2LA. (e) CPNLA.

Figure 2: Positive-edge-triggered flip-flop designs. Transistor sizes are labeled as in Fig.

1. (a) PPCFF. (b) SSAFF. (c) SAFF. (d) MSAFF. (e) HLFF. (f) HLSFF.

(g) SSAPL. (h) SSASPL. (i) CCPPCFF.

For the most part, the power usage of flip-disappointment and lock plans has been assessed using an ungated clock and few information inception plans. Taking everything into account, we get a more exact framework where each conceivable state (e.g., clock regard, input regard, yield assessment) of the TE are tallied and the energy use of each state change is assessed. A couple of

plans perform incredibly well in explicit frameworks, yet inconceivably inadequately in others. For example, in test

2 the low power SSAFF design uses on different occasions less energy than the HLFF structure, yet in test 3 it uses on various occasions more energy. Another certified outline of a TE specific for a working framework is CPNLA. This lock set up is by a wide edge the best choice for test 3 yet by far the most perceptibly awful choice in any leftover cases.

Finally, CCPPCFF [see Fig. 2(i)] is a prohibitive planning flip-flop reliant on the arrangement presented in, which consequently is an improvement. The goal of this arrangement is to diminish energy when the data doesn't change by gating the clock inside the flip-flop.

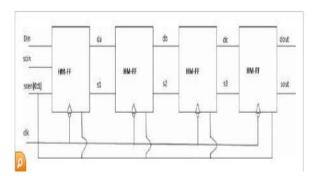

# **Move Register using HM-FF**

Successive in Serial out (SISO) Shift Register can be created by using Single Clock beat With Hold Mode (HM-FF) Flip disappointment. This sort of move register recognizes data successively for instance a tiny smidgen at a time and produces set aside information on its yield consecutively. Here, four Single Clock beats With Hold Mode (HM-FF) Flip lemon are fell. Since each HM-FF can store simply a tiny smidgen, the register can store the most noteworthy four pieces. More flip lemon can be tumbled to store various pieces. Check is applied in a singular chance to all flip disappointments timing them all the while. It has an additional sign called Scan enable Signal and it is of the two-line —select signal. The Scan engage signal picks the yield signal. The standard favored situation of using Scan enable is that it picks simply explicit yield in a period, hence timing delay is reduced.

In an HM Flip Flop, the yield is indistinct from the commitment for a heartbeat time delay and at the same heartbeat time delay, the yield will remain the same as the unaltered yield. Accordingly,

the delay is decreased for instance it will take one clock heartbeat to move the piece to the entire flip lemon.

Move register using Single clock beat With Hold Mode (HM-FF) Flip lemon alone check is applied for as a rule move undertakings and consequently, timing delay is diminished, stood out from the move register using D-FF.

Move Register using WHM -FF

Successive in Serial out (SISO) Shift Register can be created by using Single Clock beat Without Hold Mode (WHM-FF) Flip lemon. The action of the Shift register resembles that of the Shift register using HM —FF beside the yield enable work, here the compass engage signal is the individual line —select signal, anyway the action of move register is the same as that of the Shift register using HM-FF. The solitary favored situation of using this Shift register with WHM-FF is that it reduces the region overhead as shown in [1].

In Shift register using Single Clock beat Without Hold Mode (WHM-FF) Flip lemon, a singular clock, and single sign line-select is applied for by and large move undertakings. Here arranging delay is lessened, appeared differently to the move register using D-FF and HM –FF.

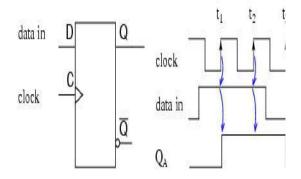

Consecutive in, successive out move registers defer data by one clock time for each stage. They will store a hint of data for each register. A successive in, consecutive out move register may be one to 64 pieces in length, longer if registers or packages are fell. Coming up next is a single-stage move register getting data that isn't synchronized to the register clock. The "data in" at the D pin of the sort D FF (Flip-Flop) doesn't change levels when the clock changes from low to high. We may have to synchronize the data to a system-wide check-in a circuit board to improve the trustworthiness of an automated reasoning circuit

Volume 9, Issue 02, February-2024, <a href="http://ijmec.com/">http://ijmec.com/</a>, ISSN: 2456-4265

The prominent moment that (appeared differently with the figure under) appeared above is that whatever "data in" is accessible at the pin of a sort D FF is transferred from D to yield Q at clock time. Since our model move register uses positive edge tricky limit parts, the yield Q follows the D information when the clock changes from low to high as shown by the up jolts on the blueprint above. There is no vulnerability to what reasoning level is accessible at check time considering the way that the data is consistent well when the clock edge. This is just every once in a while the case in multi-stage move registers. Notwithstanding, this was a straightforward manual to start with. We are simply stressed over the positive, low to high, clock edge. The falling edge can be ignored. It is very easy to see Q follow D at clock time above. Differentiation this with the outline underneath where the "data in" appears to change with the positive clock edge.

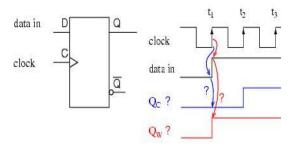

Since "data in" appears to changes at clock time t1 above, what does the sort D FF see at clock time? The short misshaped answer is that it sees the data that was accessible at D before the clock. That is what is transferred to Q at clock time t1. The correct waveform is QC. At t1 Q goes to zero if it isn't presently zero. The register doesn't see a one until time t2, at which time Q goes high

Since data, above, present at D is planned to Q at clock time, and Q can't change until the accompanying clock time, the FF concedes data by one clock period, given that the data is currently synchronized to the clock. The Waveform is identical to "data in" with one clock period delay.

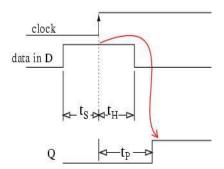

A more positive look at what the commitment of the sort D Flip-Flop sees at clock time follows. Imply the figure underneath. Since "data in" appears to changes at clock time (above), we need extra information to sort out what the D FF sees. If the "data in" is from another move register stage, another identical sort D FF, we can arrive at a couple of deductions subject to data sheet information. Producers of automated reasoning make available information about their parts in datasheets, some time back only open in a grouping called a data book. Data books are up 'til now available; in any case, the maker's site is the high-level source.

tS is the planned time, the time data ought to be accessible before clock time. For the present circumstance, data ought to be accessible at D100ns before the clock. Also, the data ought to be held for hold time tH=60ns after clock time. These two conditions ought to be met to constantly clock data from D to Q of the Flip-Flop.

There is no issue meeting the course of action period of 60ns as the data at D has been there for the whole past check time span if it comes from another move register stage. For example, at a clock repeat of 1 Mhz, the clock time period is 1000 µs, a ton of time. Data will truly be

accessible for 1000µs going before the clock, which is much more unmistakable than the base required tS of 60ns.

The hold time tH=60ns is met considering the way that D related with Q of another stage can't change any faster than the inciting deferment of the past stage tP=200ns. Hold time is met as long as the multiplication delay of the past D FF is more significant than the hold time. Data at D driven by another stage Q won't change any speedier than 200ns for the CD4006b.

To summarize, yield Q follows input D at nearly clock time if Flip-Flops are fell into a multistage move register.

Three sort D Flip-Flops are fell Q to D and the tickers took after to outline a three-stage move register above.

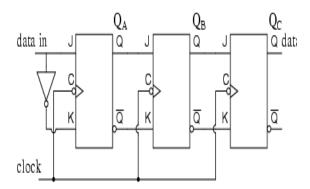

Type JK FFs fell Q to J, Q' to K with checks relating to yield a substitute sort of the move register above.

A consecutive in/successive out move register has a clock input, a data input, and a data yield from the last stage. Generally speaking, the other stage yields are not available Otherwise, it would be a consecutive in, equivalent out move register...

The waveforms under apply to both of the initial two types of the successive in, consecutive out move register. The three arrangements of jolts show that a three-stage move register

momentarily stores 3-snippets of data and concedes it by three clock periods from the commitment to yield.

At clock time t1 a "data in" of 0 is planned from D to Q of all of the three stages. In particular, D of stage A sees a logic0, which is coordinated to QA where it stays until time t2.

At clock time t2 a "data in" of 1 is planned from D to QA. At stages, B and C, a 0, dealt with from going before stages are planned to QB and QC.

At clock time t3 a "data in" of 0 is planned from D to QA. QA goes low and stays low for the extra clocks due to "data in" being 0. QB goes high at t3 on account of a 1 from the last stage. QC is still low after t3 as a result of a low from the past stage.

QC finally goes high at clock t4 on account of the high dealt with to D from the past stage QB. All past stages have 0s moved into them. Additionally, after the accompanying clock beat at t5, all reasoning 1s will have been moved out, replaced by 0s.

The rest of the report is composed as follows: area 2 portrays the designing of the proposed move register. Segment 3 presents the assessment delayed consequences of the

# **Performance Comparison**

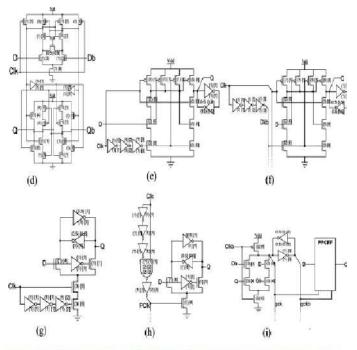

The semiconductor connection of beat snares and flip-flops. The transmission entryway beat lock (TGPL) [7], mutt snare flip-flop (HLFF) [8], unforeseen push-pull beat lock (CP3L) [9], Power-PC-style flip-flop (PPCFF) [10], Strong-ARM flip-flop (SAFF) [11], data arranging flip-flop (DMFF) [12], prohibitive recharge sense-speaker flip-flop (CPSAFF) [13], prohibitive catch flip-flop (CCFF) [14], flexible coupling flip-flop (ACFF) [15] are differentiated and the SSASPL [6] used in the proposed move register.

The schematic of the PPCFF, which is an ordinary master-slave flip-flop, made out of two snares. The PPCFF includes 16 semiconductors and has 8 semiconductors driven by clock

signals. For a sensible assessment, it uses the base size of semiconductors. The proportions of NMOS and PMOS semiconductors are  $0.5\mu m/0.18\mu m$  and,  $1\mu m/0.18\mu m$  independently. Its plan was drawn moderately by sharing each and every comprehensible source and drains of semiconductors. All circuits were completed with a  $0.18\mu m$  CMOS measure. The powers were assessed at VDD=1.8V and fCLK=100MHz.

The presentation connections of the PPCFF and SSASPL. The SSASPL is 48.8% more unobtrusive and consumes 60.2% less power than the PPCFF.

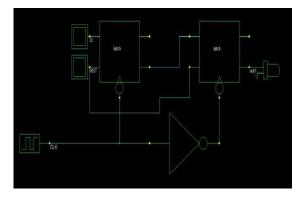

The presentation connections of the 256-bit move registers. The normal move register using flipflops was executed with the PPCFFs. Two sorts of the proposed move register using beat locks were realized with the SSASPLs. The proposed move register achieves a little district and low power use diverged from the normal move register.

The domains of the proposed move registers with K=4 and K=8 are 63.2% and 59.0%, exclusively, diverged from that of the standard move register. The power usages of the proposed move registers with K=4 and K=8 are 56.3% and 56.5%, exclusively, appeared differently in relation to that of the standard move register.

Volume 9, Issue 02, February-2024, <a href="http://ijmec.com/">http://ijmec.com/</a>, ISSN: 2456-4265

#### **EXPERIMENTAL RESULTS**

The proposed 256-digit move register with K=4 was made using a  $0.18\mu m$  CMOS measure. Table 3 records the features of the move register chip. The chip has  $6600\mu m2$  and consumes 1.2mW at VDD=1.8V and fCLK=100MHz.

Fig. 2.15 shows a microphotograph of a chip. Figs. 2.16 (a) and 2.16 (b) show the conscious waveforms of the move register at fCLK=100MHz and fCLK=10MHz, separately. In the entertainments, the move register with K=4 works up to fCLK=840MHz, yet in the assessments, the clock repeat was 100 MHz due to the repeat furthest reaches of the preliminary stuff. Fig. 2.16(a) addresses a clock indication of 100 MHz, an information signal (IN), two yield signals from the chief sub move resister (Q1 and Q2). Fig. 2.16(b) gives a clock indication of 10 MHz, a data signal (IN), eight yield signals from the first and second sub move resisters (Q1-Q8), and the last caution sign of the 256-bit move register (Q256).

#### **CONCLUSION**

In this study, a shift register that makes use of pulsed latches is offered as a space- and power-saving alternative. The shift register supplants flip-flops with pulsed latches, which results in a significant reduction in both space requirements and power consumption.

Multiple, non-overlapping delayed pulsed clock pulses, rather than a single pulsed clock signal, are used to alleviate the timing issue between pulsed latches. By organizing the latches into numerous sub-shifter

ISSN: 2456-4265

IJMEC 2024

registers and making use of additional temporary storage latches, just a subset of the pulsed clock signals is consumed. Fabrication of a 256-bit shift register was accomplished utilizing a 0.18-micron CMOS process and VDD=1.8V. Its central area is 6600 m2. At a 100 MHz clock frequency, it uses 1.2 milliwatts of power. When compared to a traditional shift register that uses flip-flops, the suggested shift register reduces both space requirements and power consumption by 37% and 44%, respectively.

#### REFERENCES

- [1] P. Reyes, P. Reviriego, J. A. Maestro, and O. Ruano, "New protection techniques against SEUs for moving average filters in a radiation environment," IEEE Trans. Nucl. Sci., vol. 54, no. 4, pp. 957–964, Aug. 2007.

- [2] M. Hatamian et al., "Design considerations for gigabit ethernet 1000 base-T twisted pair transceivers," Proc. IEEE Custom Integr. Circuits Conf., pp. 335–342, 1998.

- [3] H. Yamasaki and T. Shibata, "A real-time image-feature-extraction and vector-generation vlsi employing arrayed-shift-register architecture," IEEE J. Solid-State Circuits, vol. 42, no. 9, pp. 2046–2053, Sep. 2007.

- [4] H.-S. Kim, J.-H. Yang, S.-H. Park, S.-T. Ryu, and G.-H. Cho, "A 10-bit column-driver IC with parasitic-insensitive iterative charge-sharing based capacitor-string interpolation for mobile active-matrix LCDs," IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 766–782, Mar. 2014.

- [5] S.-H. W. Chiang and S. Kleinfelder, "Scaling and design of a 16-megapixel CMOS image sensor for electron microscopy," in Proc. IEEE Nucl. Sci. Symp. Conf. Record (NSS/MIC), 2009, pp. 1249–1256.

- [6] S. Heo, R. Krashinsky, and K. Asanovic, "Activity-sensitive flip-flop and latch selection for reduced energy," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 9, pp. 1060–1064, Sep. 2007.

- [7] S. Naffziger and G. Hammond, "The implementation of the nextgeneration 64 b itanium microprocessor," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2002, pp. 276–504.

### **AUTHOR PROFILE**

**Ms. NAGAMANI MOUNIKA**, M.Tech student in ECE (VLSI System Design) from Shadan College of Engineering And Technology, Peerancheru, Telangana.

ISSN: 2456-4265

**IJMEC 2024**

**DR. MOHAMMAD ILIYAS** working as **Professor & HOD** of **ECE Department** and **Dean** (**Academics**) at Shadan College of Engineering and Technology, Hyderabad. He received his Bachelor degree in Electronics and Communication Engineering from J.N.T.U.H affiliated college, Hyderabad, M.Tech, V.L.S.I System Design from J.N.T.U.H affiliated college. He has completed Ph.D from Sunrise University. His research interest is Low power VLSI Design.

Dr. AMAIRULLAH KHAN LODHI, Professor, ECE Department, and Dean (R & D) from Shadan College of Engineering and Technology, Peerancheru, Telangana.